本篇文章延续前一个篇《FPGA杂记基本篇》,随时为同学们分享到IP例化和几块为FPGA集成电路芯片变现的Demo过程中。IP在于一封安装好的传感器,整合在相对应的开拓坏境里边儿,以安路的TD免费APP实例,各种有差异 系列表的IC芯片整合了各种有差异 的IP传感器,需要依据免费APP例化获取。

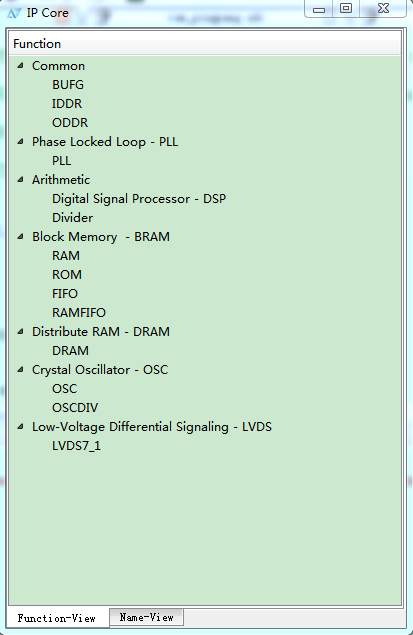

这是安路TD4.6.5模块化的EF3L40CG332B的有关IP。

1.1 PLL&RAM

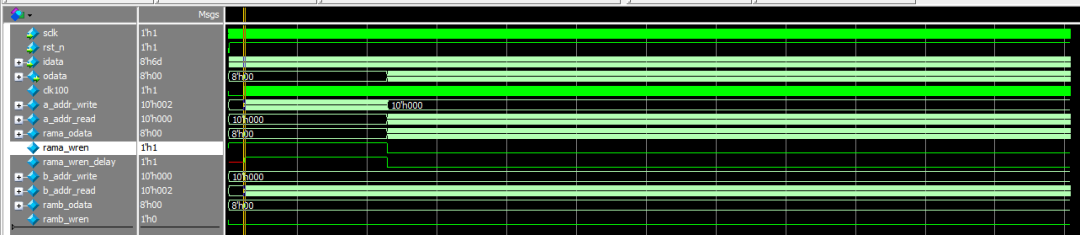

以例化PLL和RAM试对,实现目标两种异步双口 RAM。

读写闹钟都安装 100Mhz, 好几个 RAM 为 RAMA 和RAMB, 深入为 1024,位宽为 8bit,拷贝信息资料为 8bit,100Mhz 长期信息资料流, 当 RAMA被拷贝 1024 字节信息资料后调节桌面到写 RAMB, RAMB 被拷贝 1024 字国庆中秋调节桌面 RAMA。当以循环系统类推。

当 RAMA 被读入 1024 字节时, 给读时序保证某个开始资料源读 RAMA 的资料源, 读完 RAMA 的 1024 字节资料源时, 设置读 RAMB 以类推。

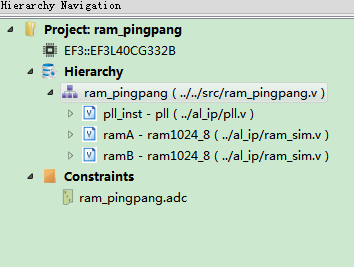

这家市政工程建设的市政工程建设空间结构有以下图:

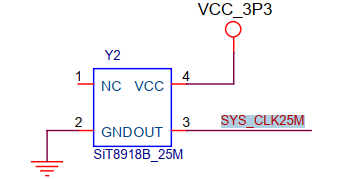

第一个EF3L40CG332B_DEV开放板展示 了25Mhz的晶振钟表投入到EF3L40CG332B的钟表管脚。

都想得以100Mhz的读写传输速率,必须要先用PLL得以倍频挂钟。

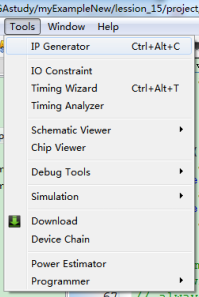

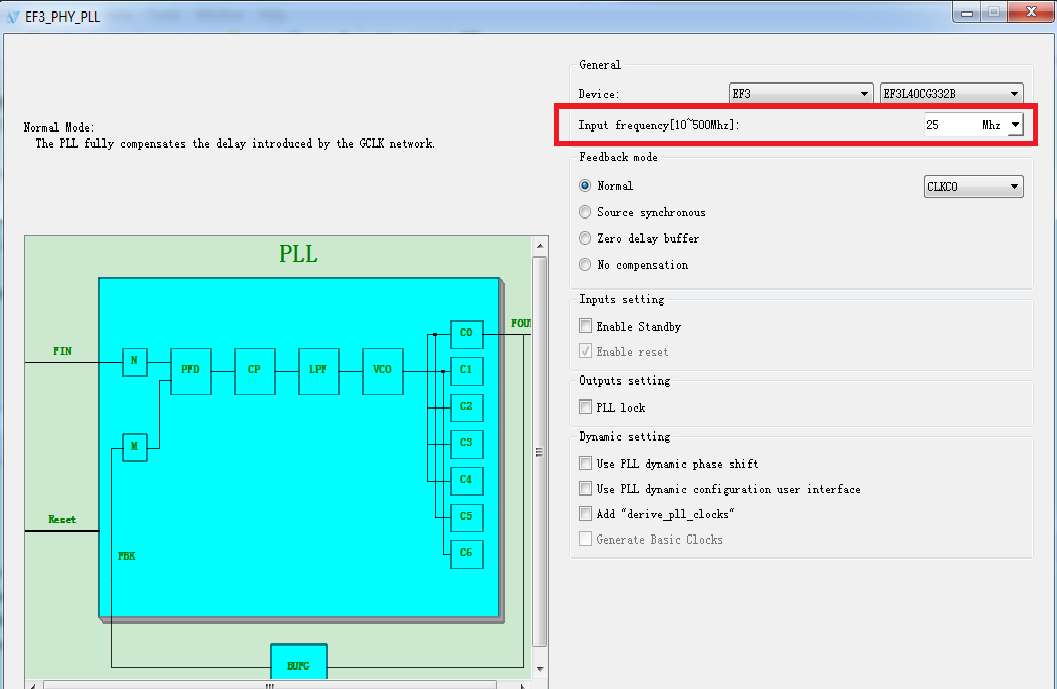

在tools列表下弹窗IP Generator打开IP core页面设置,并选泽PLL,投入秒表添上板子晶振25Mhz。

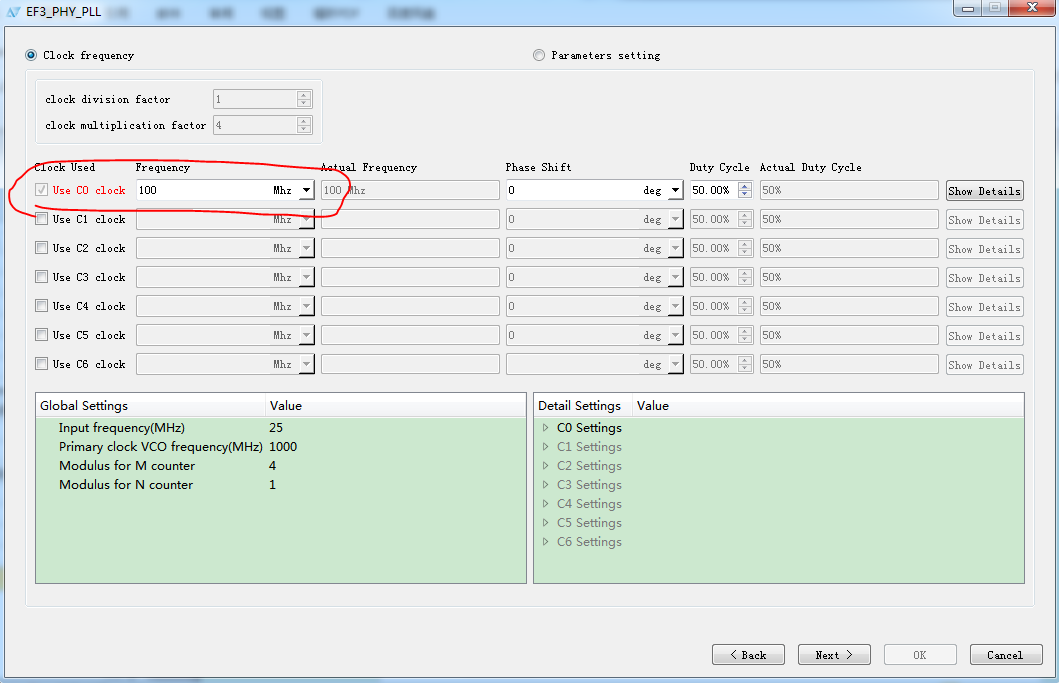

工作工作输出石英钟填到必备要的100Mhz,并从C0工作工作输出。

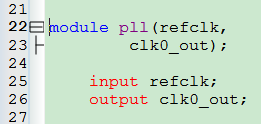

设备成功完成后,形成的module声明函以下的(完整的板块可选取编号)

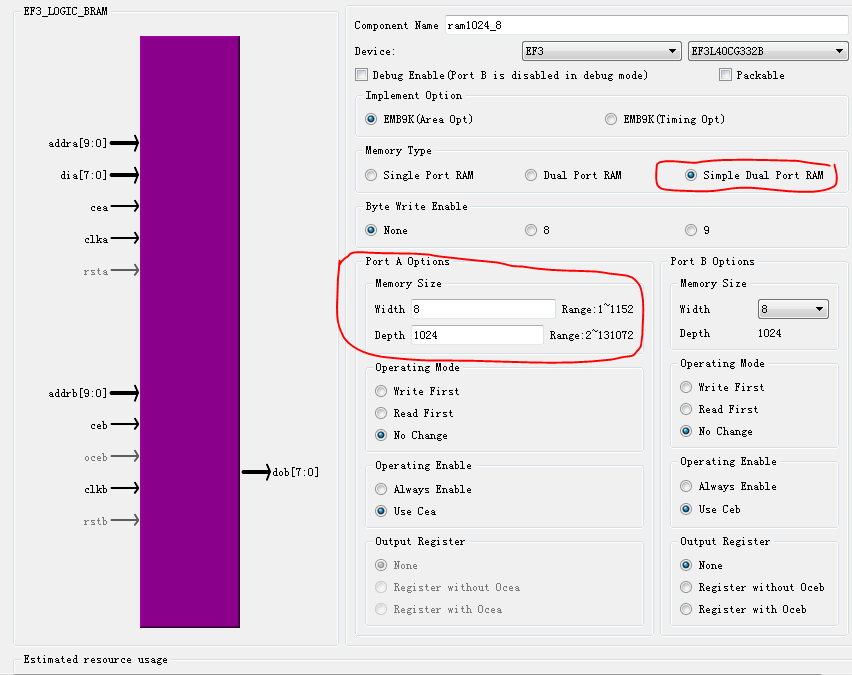

再造成ram的IP接口

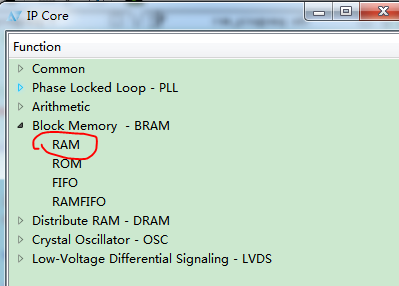

在IP core填入择RAM

Memory type选择简单双口ram,memory size设置位宽8bit深度1024

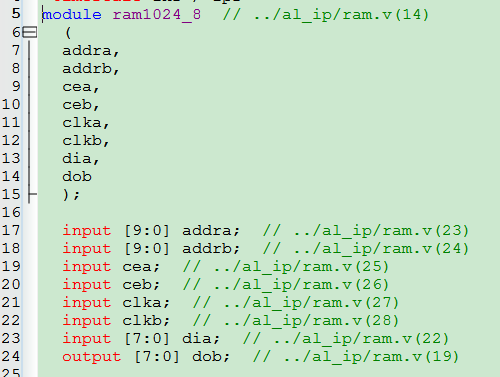

配置成功后,转化成的module证明内容如下(完全控制模块可选取代码怎么用)

然后呢编撰层顶文档还有就是在层顶例化PLL和RAMA、RAMB。

顶层楼系统文件中核心是对ram的复制粘贴口实现时序操作的,涵盖ramA、ramB的读详情IP地址,写详情IP地址、使能表现和复制粘贴导出信息,详情二维码读书笔记中不要赘述,能就直接符合二维码。

可全方位的组件电源制定出提交后,制定出模型仿真模拟技术组件电源并便用模型仿真模拟技术系统软件开始模型仿真模拟技术。

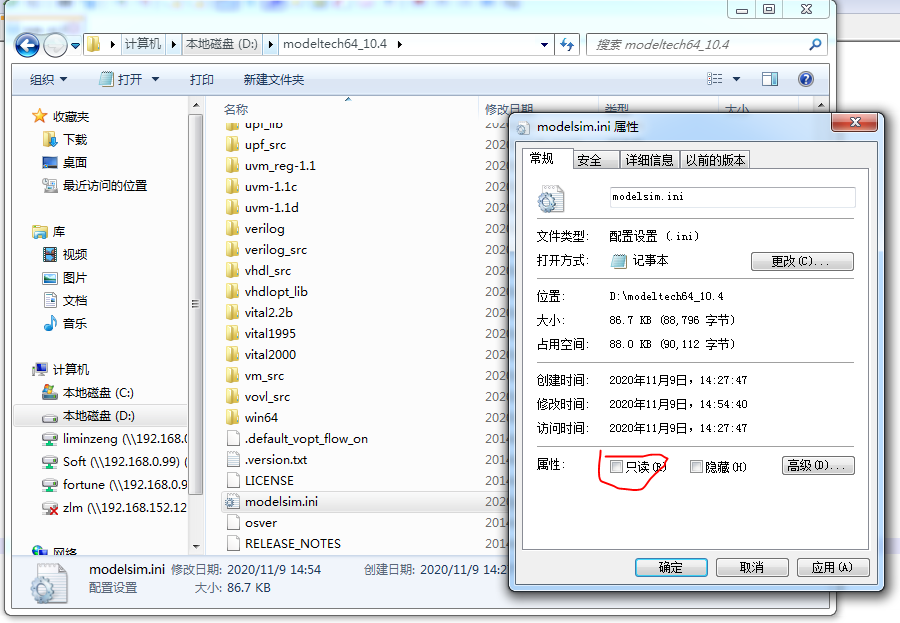

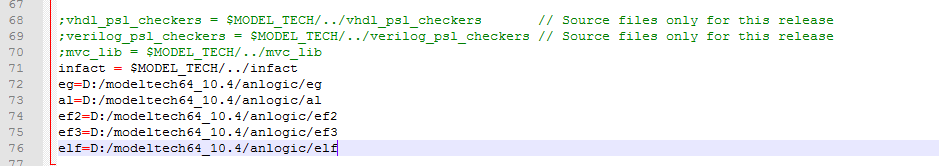

犹豫我局工程施工用到等到安路的IP库,所以说也所需在modelsim中增长相对应的安路模型仿真库,增长技术相应:

先要在modelsim的进行安装分类目录底下复制modelsim的缺省化信息modelsim.ini,右键技能后,将它的只读技能退出,然而用文信息(本市政工程在使用的是notepad++)复制。

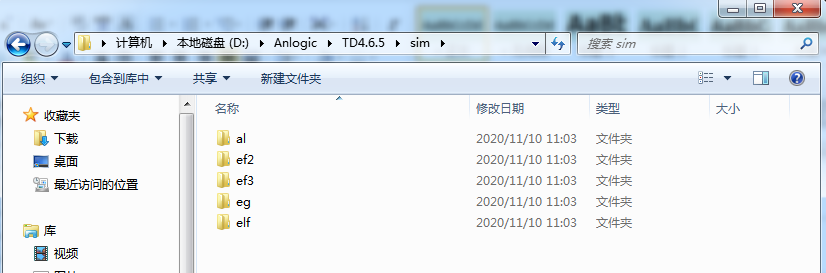

在modelsim.ini的[library]文书名录列表下修改安路的模仿库文书名录名录,安路所以的模仿库文书名录也在安路的编译小软件TD装配名录下的sim文书名录夹中,在此将其所以的库文书名录都借鉴进了modelsim的文书名录夹里,若不借鉴,也可直接性手机输入安路文书名录夹的相对路径。

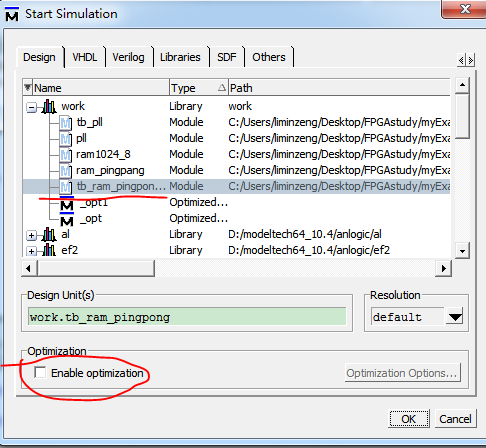

保存后退出,打开modelsim并创建工程,编译通过后,进入仿真步骤,在simulate状态栏下选择start simulate,如下图:

选模拟仿真的上层而且封升级优化按钮。

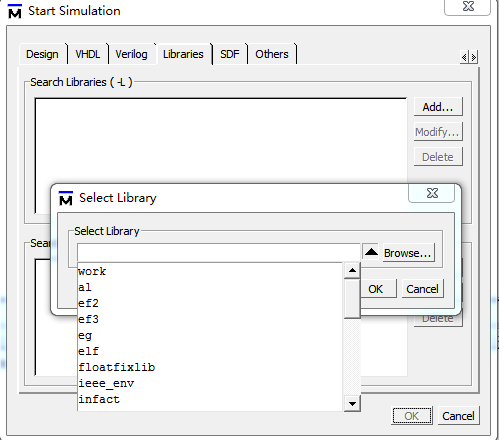

同一时间个对话框开启libraries页面内容并在search libraries栏右测使用add,下拉列表页使用相对的ef3的库系统文件。

设为成功后点击量OK流入逼真必须。

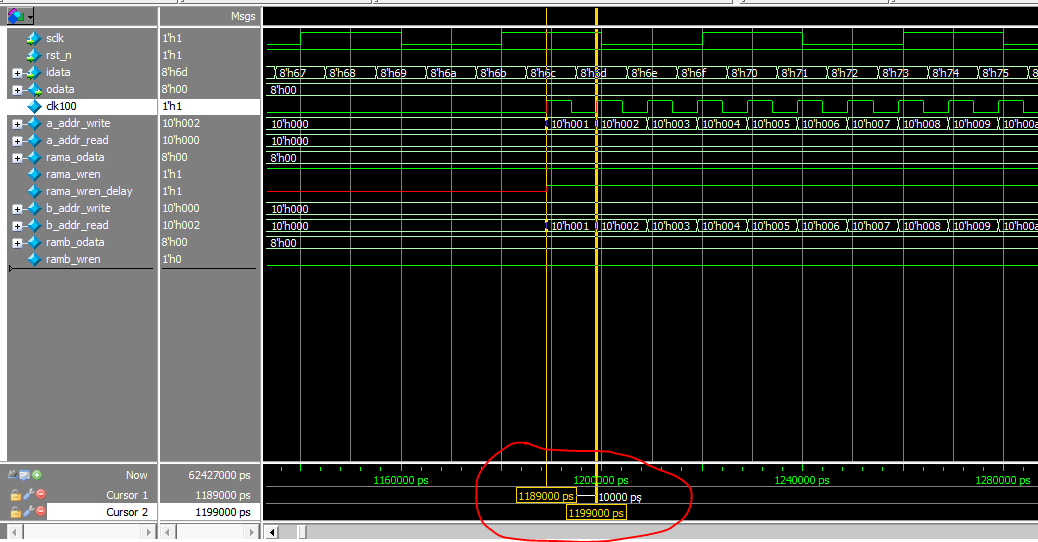

此前实验所中遇上现象和校准下面的:

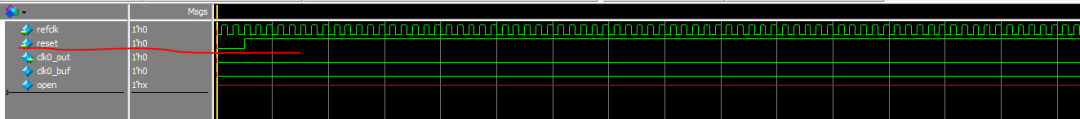

刚已经开始pll就没有输出精度走势,于是点开了pll察看正弦波形参数出现 pll正弦波形参数下面的:

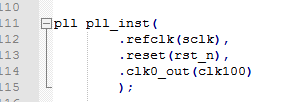

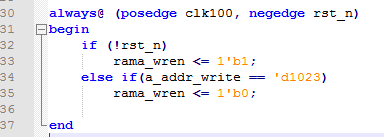

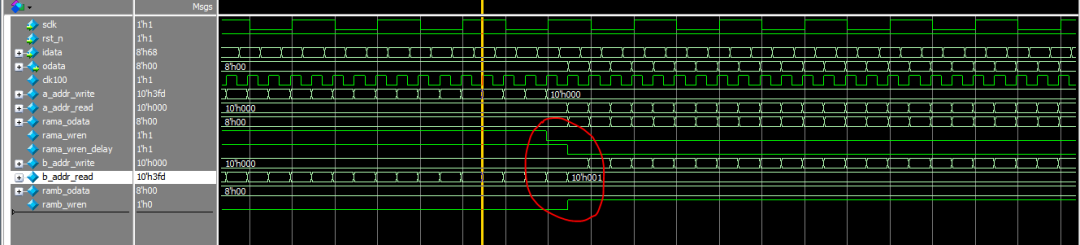

表明了是置位了reset移动信号导至的,观察编号表明了如下图所示:

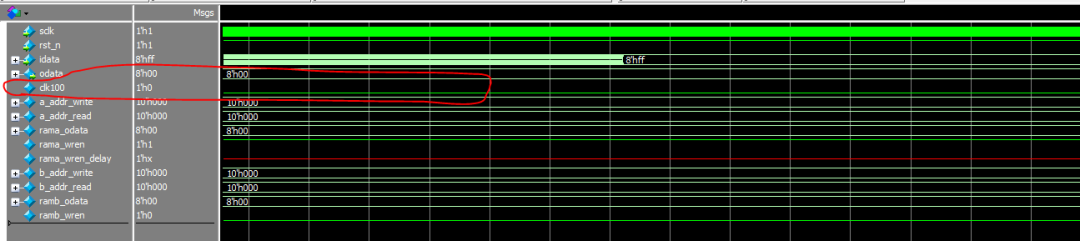

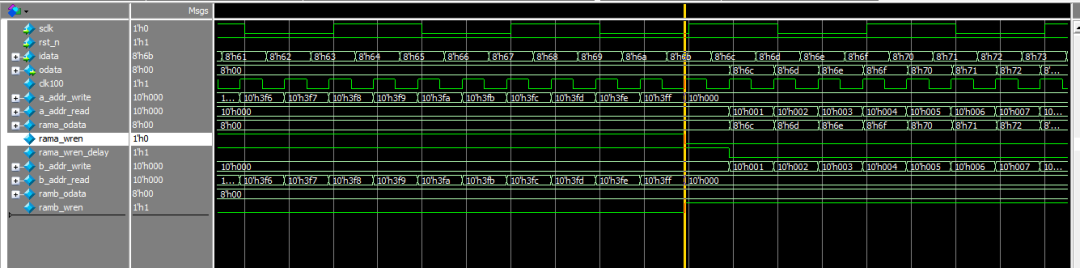

回位卫星移动网络数字信号灯立即链接 到pll的置位卫星移动网络数字信号灯,随着回位卫星移动网络数字信号灯是低电平有郊而置位卫星移动网络数字信号灯是高电平有郊,之所以导至了pll直正处在回位的情况发生。改成后,立即将pll回位卫星移动网络数字信号灯置0,二维码和防真最后通常,下述所显示:

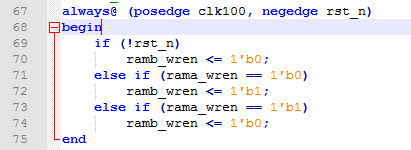

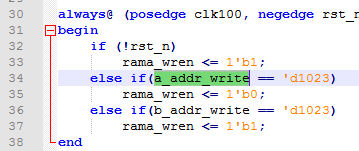

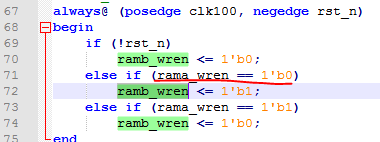

基本气象观测就能够发掘,rama读使能数据只提升了了次,而ramb的读使能时常没办法跳变,跳转代碼查询发掘:

思想判段时未将rama的写使能移动信号置1的经济条件标出来。

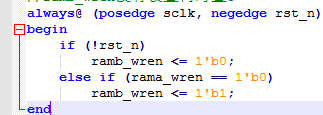

ramb的写使能一样:

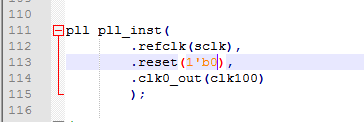

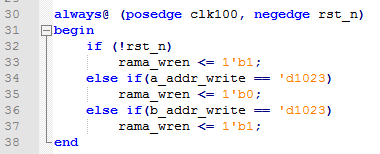

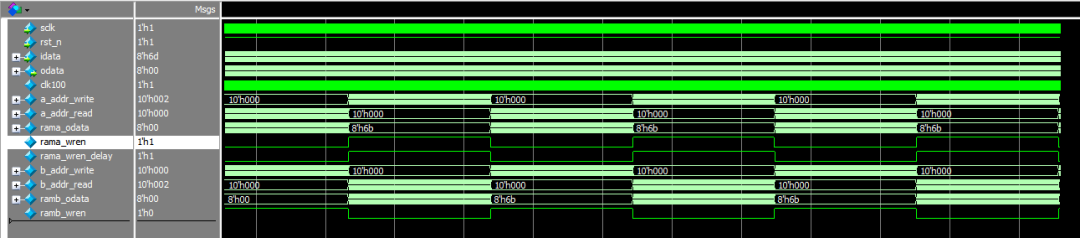

粗看总体完全符合rama、ramb变化读写的功能模块,测量rama、ramb时序变化详情。

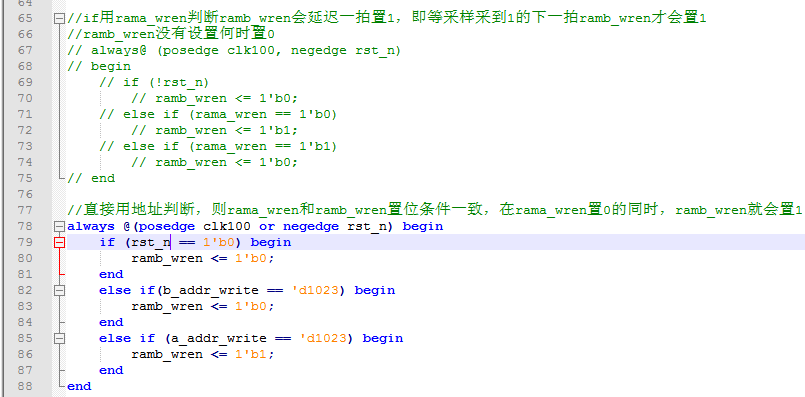

在rama和ramb写使能手机信号更换时,出现空一个多拍,再观察源代码,出现rama、ramb写使能在具体条件答案时,实用的答案原理也不一个的,出现ramb_wren的置位会在rama_wren置位后的下拍一拍参与。

因为改换ramb_wren的判别生活条件,使之与rama_wren的一样的,都以写详细地址为生活条件判别再仿真模拟。

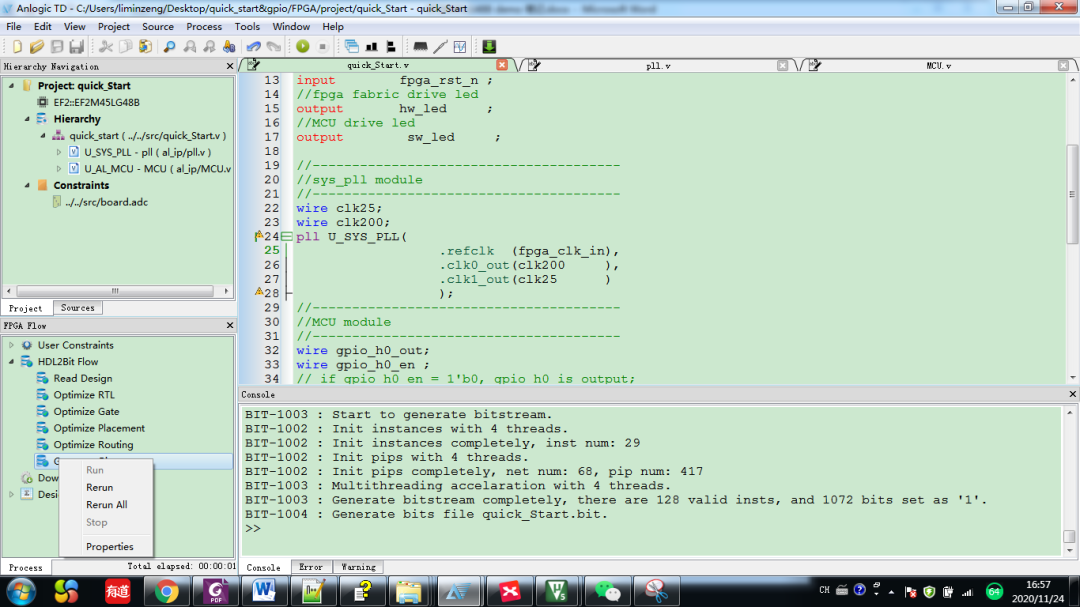

quick start & GPIO Demo

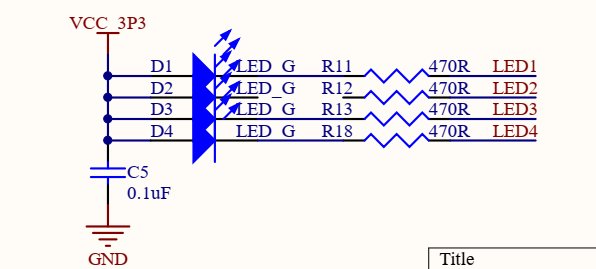

某次demo建立系统下述:FPGA操纵LED D1闪亮,MCU操纵LED D2常亮。

2.1 keil工程环境创建

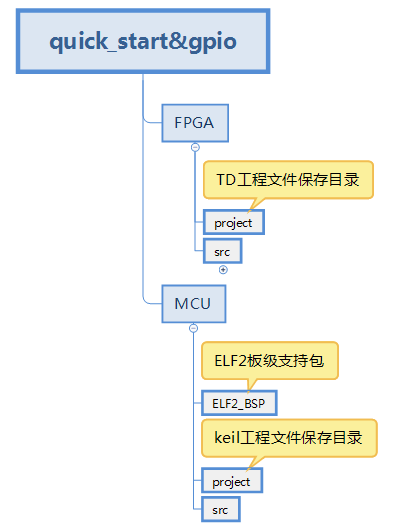

創建档案夹目次下面:

图1

之中板级支持系统包简单由原车出示。

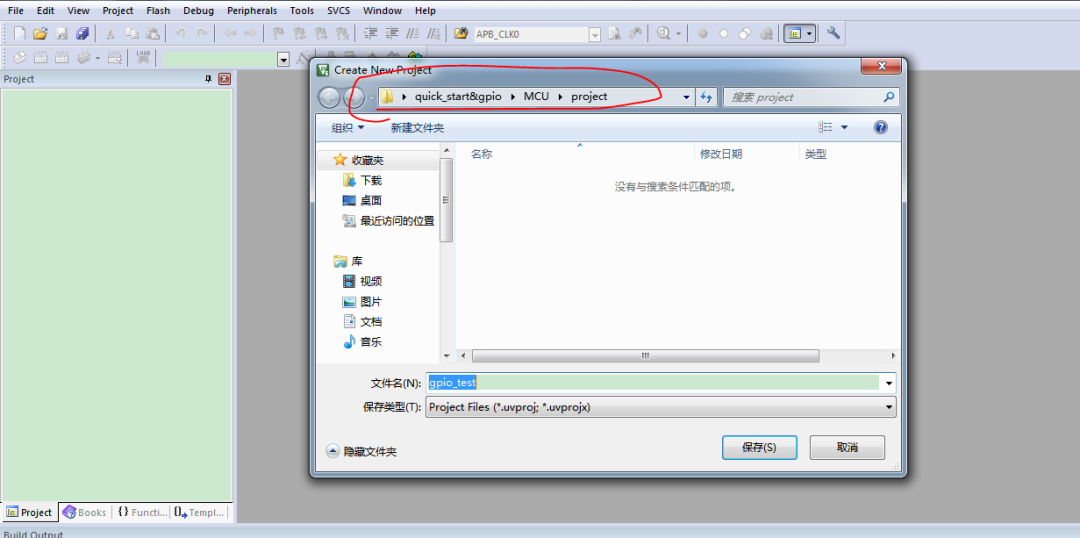

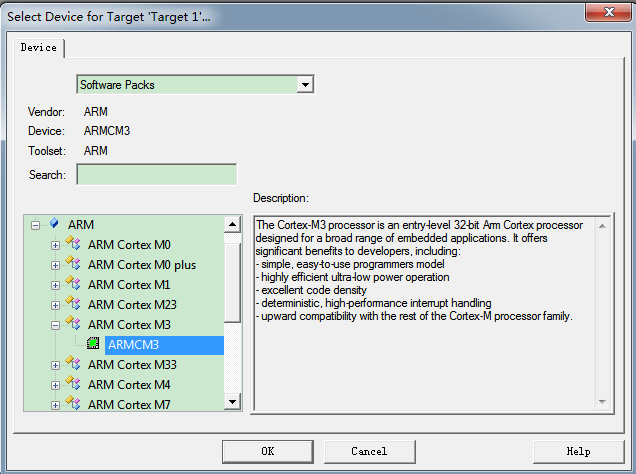

先创立keil市政工程项目,打开浏览器keil,创立市政工程项目,存有在对应着的MCU→project目录格式下。

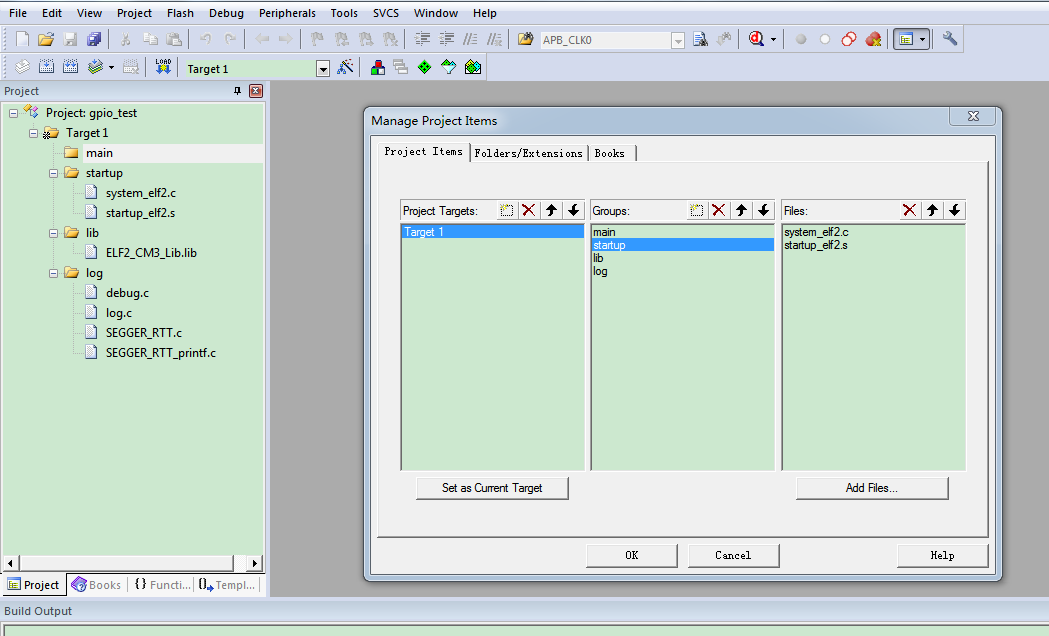

施工建好后,加入不必要的BSP包中的资料给出,建设好后的施工的目录如左栏:

其中,startup组下的文件分别来自MCU\ELF2_BSP\Device\ELF2\Source和MCU\ELF2_BSP\Device\ELF2\Source\ARM目录下;lib组的文件来自MCU\ELF2_BSP\Driver;log组文件保存在MCU\ELF2_BSP\Debug和MCU\ELF2_BSP\Debug\RTT目录下。

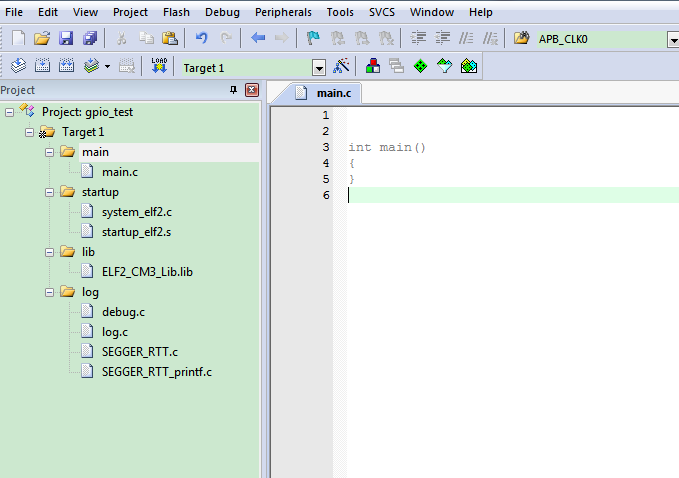

在建main.c文本并保持在图1所显示的总文本分类目录访问 的MCUàsrc文本夹下并插入main.c到工业main组中。

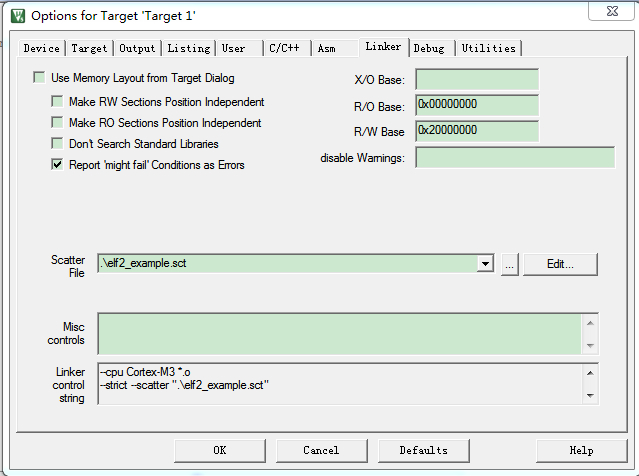

后面 设为其他工程建筑的氛围,使用 options for target经典对话框。

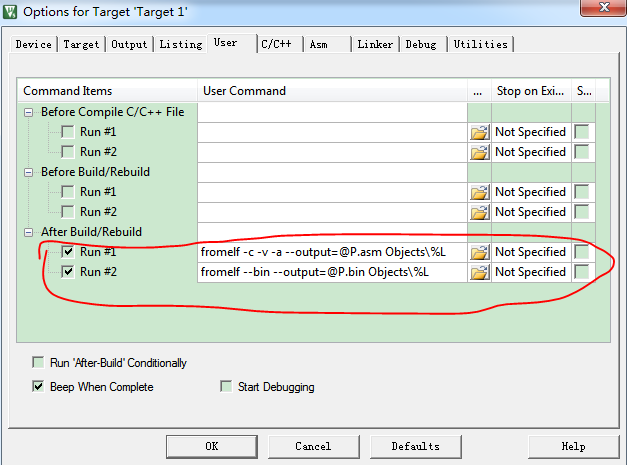

切换到user栏,设置如下参数,这些参数会影响输出keil工程的*.asm 和*.bin 文件,我们需要通过添加这两条指令得到bin文件并最终提供给FPGA。

调用的语句区分下述:

fromelf -c -v -a --output=@P.asm Objects\%Lfromelf --bin --output=@P.bin Objects\%L

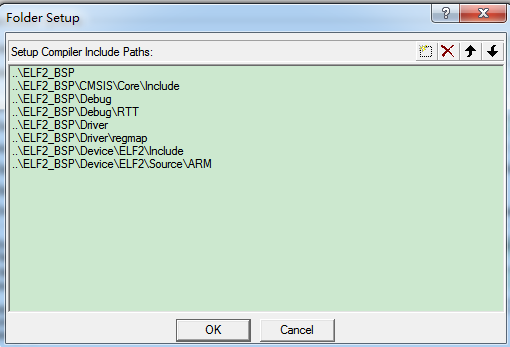

再就能到C/C++栏,装置头文档路径分析以下:

也需要直观获取一下文件目录

..\ELF2_BSP;..\ELF2_BSP\CMSIS\Core\Include;..\ELF2_BSP\Debug;..\ELF2_BSP\Debug\RTT;..\ELF2_BSP\Driver;..\ELF2_BSP\Driver\regmap;..\ELF2_BSP\Device\ELF2\Include;..\ELF2_BSP\Device\ELF2\Source\ARM

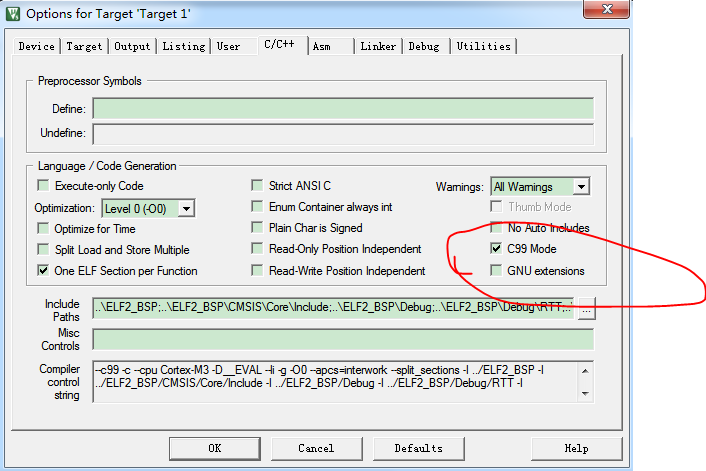

另外软件设置如下图所示图:

移除减少刷新文档文书elf2_example.sct(elf2_example.sct文档文书按照二维码可学习施工)

环境设备立即后能否开端书写过程中代碼。

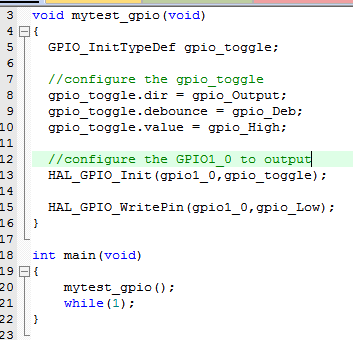

2.2 C代码编辑

在main函数公式中网站对GPIO的进行。

先对GPIO原始化结构的体赋值,再获取GPIO原始化变量,HAL_GPIO_WritePin变量对根据的GPIO做好低高赋值。

此前实用C代码怎么用对GPIO1_0的运营是置低,GPIO1_0关键代表什么意思会在下一根(1.3)实行表明。

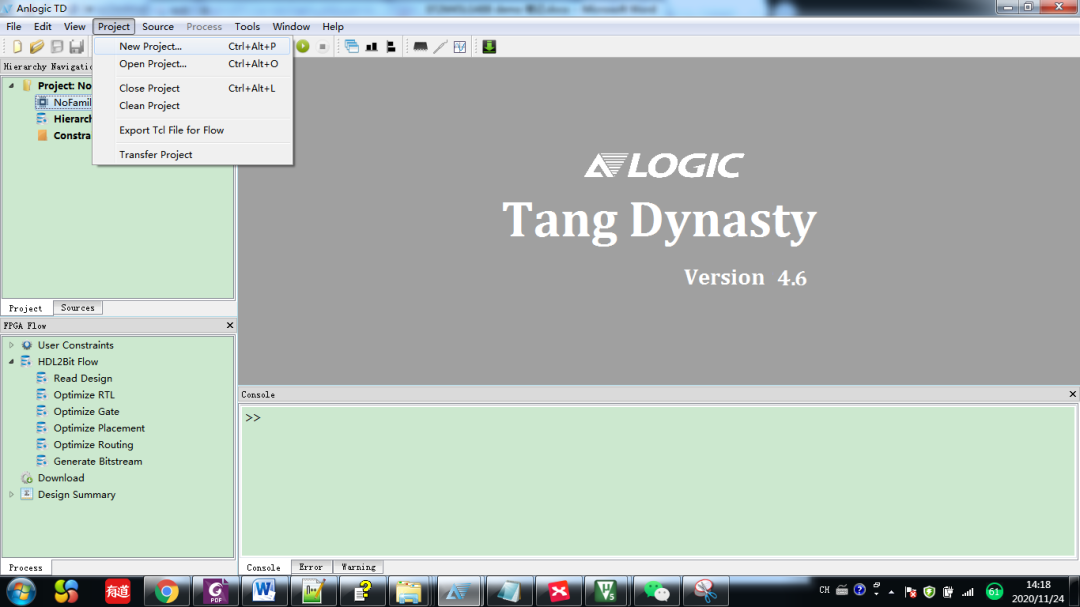

2.3 TD工程创建和代码编辑

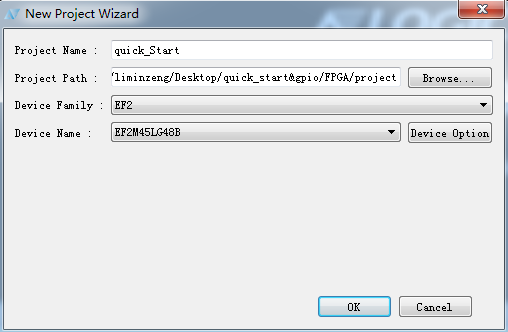

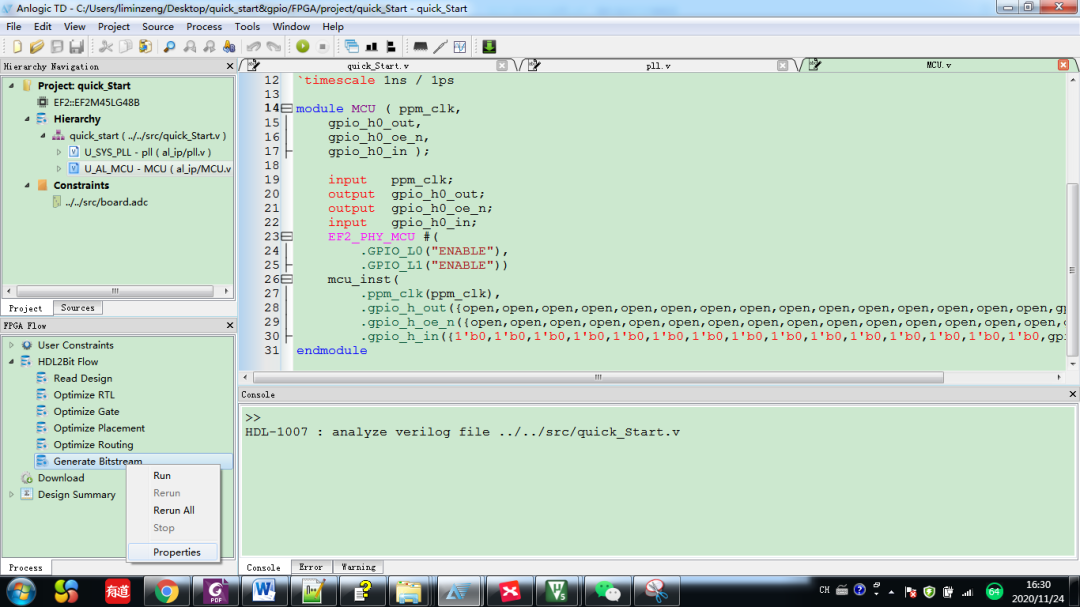

打开文档TD4.6.5或一些发行版创造新的项目 。

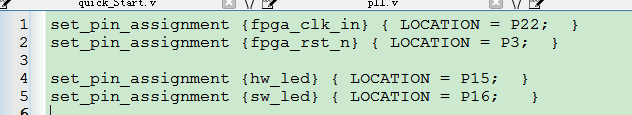

保存图片在总名录的FPGA→project名录下,并取舍相关联的功率器件类型的。

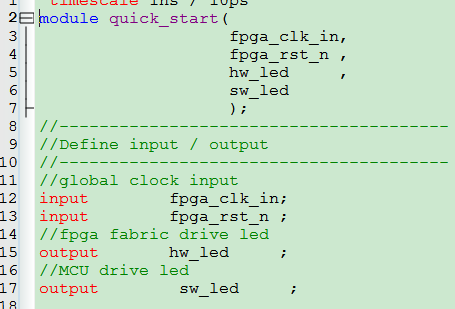

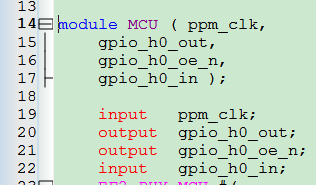

加上也许剪辑源文本,这次的项目工程摸块书面声明下列:

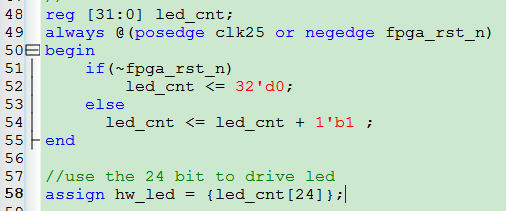

进来hw_led是由FPGA方法论管控的led,sw_led是由MCU源代码是什么怎么用管控的led(即1.2中的gpio1_0)。hw_led的管控源代码是什么怎么用相应,sw_led的管控源代码是什么怎么用详细1.2:

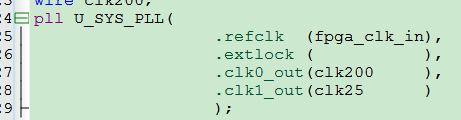

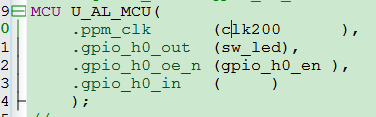

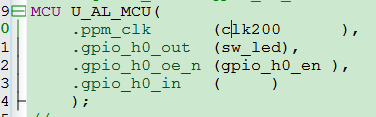

第二步例化MCU和PLL,PLL例化主要的得以键盘输入到MCU的机系统挂钟,例化期间略,这些贴上在一层中资源调用的结杲:

内容输出的200M的钟表接通MCU的机系统钟表。

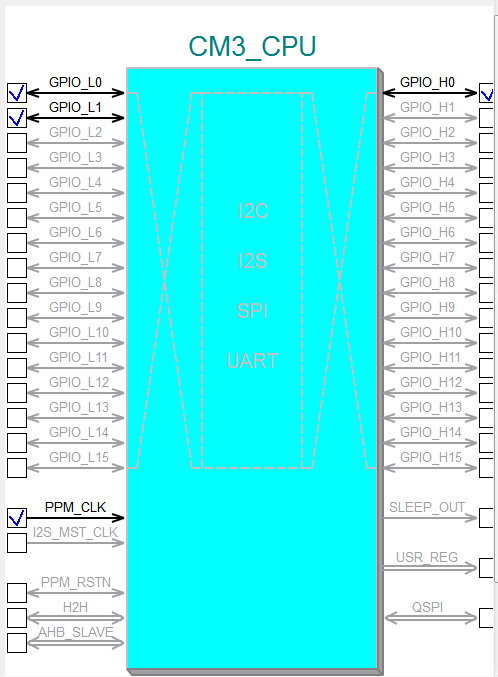

例化MCU菜单栏内容如下:

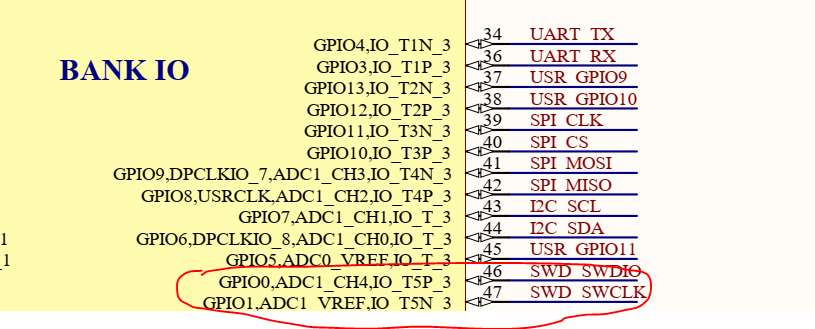

如下图如图是,MCU能够最好 32 个GPIO,在这当中低16位,即GPIO_L0~GPIO_L15是就直接相连到至pad的;而GPIOH0~GPIOH15则是顺利通过FPGA相连到至外面,但是,当选择这16个GPIO的情况,必须 在FPGA公程的教导自我约束压缩文件大拇指定具有相连到至什么脚。

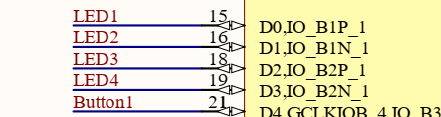

在例化MCU时,用到到那种脚就需要打开网页文档代表的按钮,这类本例中,打开网页文档了L0、L1和H0,PPM_CLK,这里面PPM_CLK是FPGA Fabric 插入石英钟,连结至FPGA的PLL读取clk200;L0、L1连结至PAD,关注原里图。

GPIO0和GPIO1联接的是测试口;还有H0联接至FPGA 中sw_led并采用管脚干涉联接至LED D2。

过程的调教参照文件下载方式:

查设计规划板的操作过程图,D2接触至FPGA的16脚,且从的操作过程图不错的察,keil工程建设中对该GPIO的的操作是置低,具体化表明是D2常亮。

并在楼房顶层中加载:

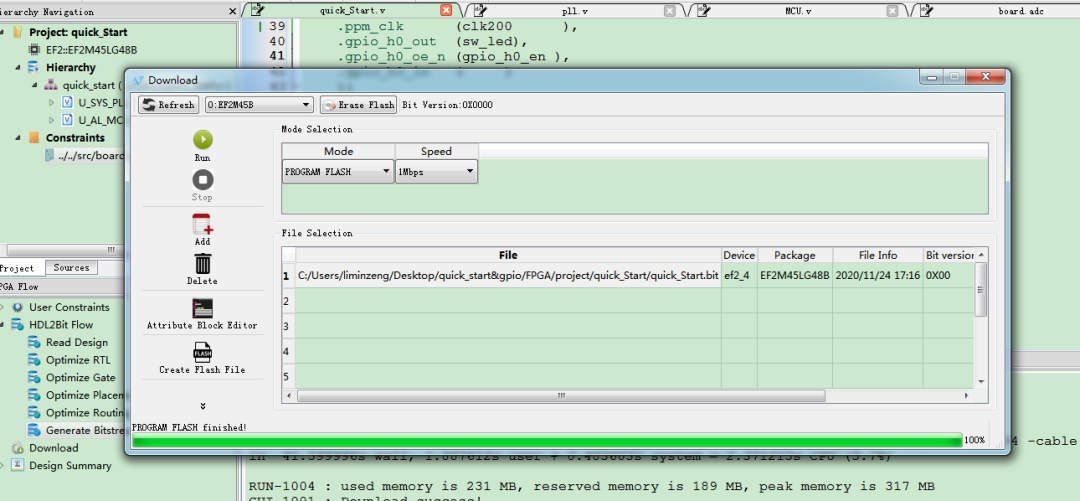

2.4 下载

Keil和TD的项目都加入编程完工后,编译项目。中间,keil制成的项目bin文本所需与TD关联性并依据TD下载地址至存储芯片或定制开发板中。

相关联的部骤方式:

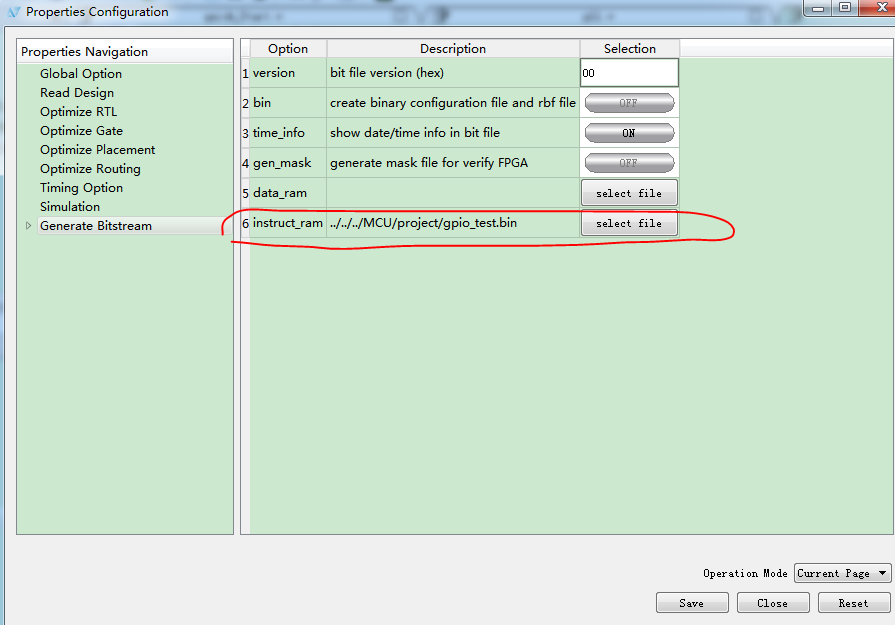

在HDL2Bit Flow栏右键选用properties。

在generate bitstream的第十项instruct ram填入择keil建设公程出现的bin文件名的目录索引(同时keil建设公程就编译按照),并保护。

保持后,双击generate bitstream编译TD公程,例如在选泽路径分析前以及编译过TD公程了,都要右键选泽rerun进行编译(留意:例如改进了keil的C文书而TD的HDL文书没了转化,推荐 也rerun后再将文书进行下载至激发板)

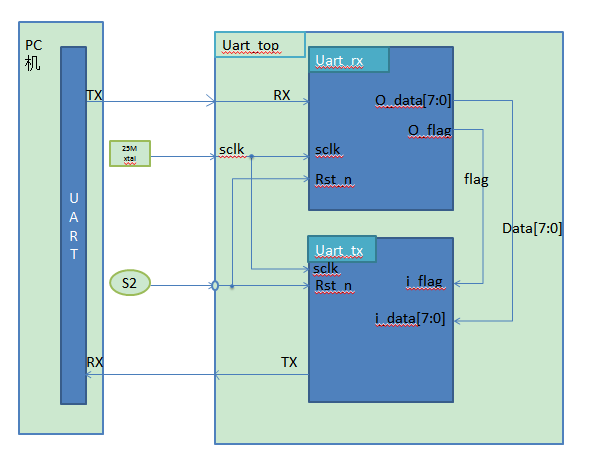

FPGA串口流量

本Demo应用案例特征提取安路的EF2M45LG48_MINI_DEV2的开发板,凭借测式板的uart口和PC机的uart口连到来产生一名反馈控制管路,即PC机运输数据分析报告至FPGA测式板,FPGA发送到并调用同样的数据分析报告。检测毕竟凭借PC机的串口校准助手下载校准看看。

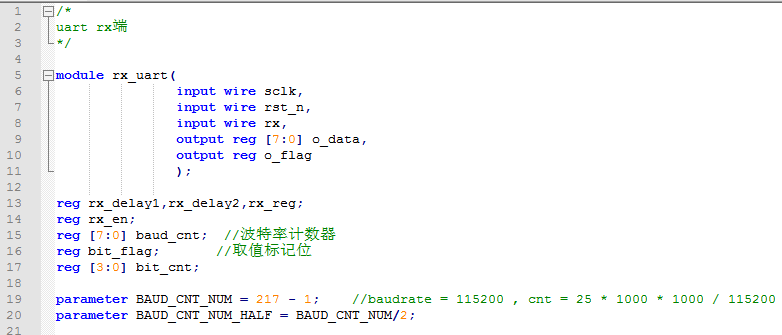

3.1 UART协议

UART 不是种互通串行统计资料信息源总线,广泛用于异步流量网络,将统计资料在串行流量网络和并行计算流量网络间的文件文件传输变换。实质的讲可是把多比特的统计资料有效的转为为单比特的统计资料(tx端),或许把单比特的统计资料有效的转为为多比特的统计资料(rx端)。做作业流程图是将统计资料的任何 bit 面接面地文件文件传输。

rx,接受到端,位宽为 1 比特, pc 机使用串口往 FPGA 发 8 比特数值时,FPGA 使用串口线 rx 位位地接受到,从至少位到是最高的位由小到大接受到,最后一步在 FPGA 里边儿位结合成8 比特数值。

tx,运输端,位宽为 1 比特, FPGA 使用串口往 pc 机发 8 比特信息时, FPGA 把 8 比特信息使用 tx 线这位这位的传染给 pc 机,从低位到最高的人位从左到右运输,后面串口通信使用串口精灵助手把这这位这位的信息位无缝拼接成 8 比特信息。

注意点:

1、串行数据源的运送和发收都最先上升楔形到上升楔形。

2、再不发布也许不阅读的统计数剧的现象下, rx 和 tx 地处空闲心态,此情此景 rx 和 tx 线都提高【高电平】,一旦有的数传言递,第一步也有同一个开始和结束位0,最后是 8 比特的的统计数剧位,随后有 1 比特的退出位(高电平),一旦退出位的时候不发的统计数剧,将开启空闲心态,要不然又将的统计数剧线变低(开启开始和结束位心态)。

3、波特率求算:uart无线接入有不一的波特率,动用HDL语音详情时,平常动用计算器来达成不一波特率的数据库营销。计算器的计算值与按照波特率相关,以通常的115200来说,假如设备数字石英钟是25Mhz,则无线接入1bit所用要的数字石英钟时间为25 * 1000 *1000 /115200 = 21七个,因而计算器计算值即216(从0逐渐计算)。

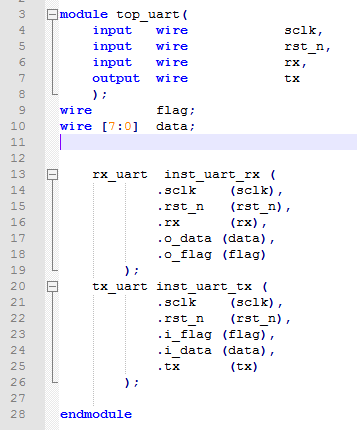

3.2 模块总框架

传感器的总体性体系结构如下图所示:

top层不仅挂钟和恢复讯号的进入,还是有进入讯号rx和输送讯号tx,依次源于PC机和输送到PC机,生成前馈。子功能中,Rx讯号再看做uart_rx功能的进入,經過uart_rx功能的办理,转化成成八位并行处理执行大数据显示o_data输送;对uart_tx功能,核心将进入的i_data并行处理执行讯号转化成成串行大数据显示再输送到PC机。

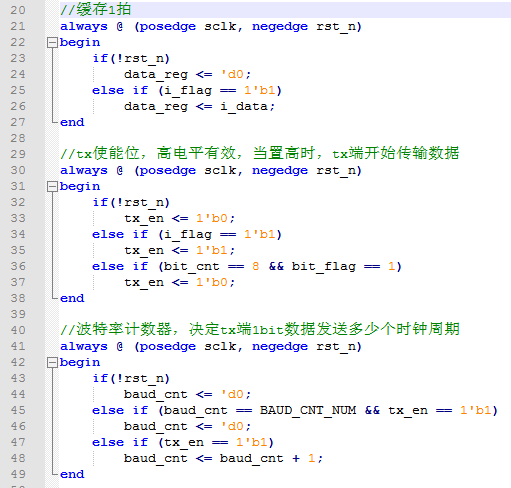

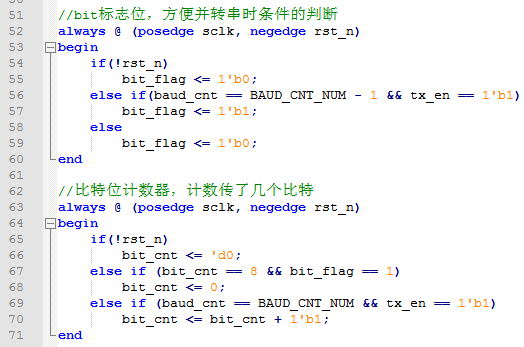

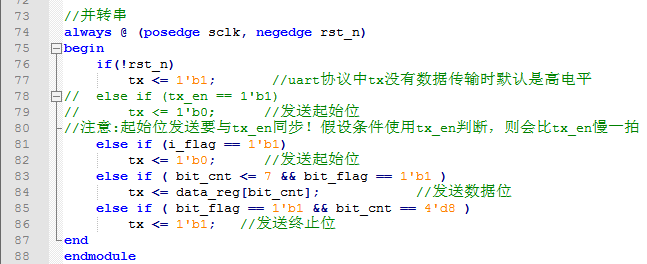

3.3 代码实现

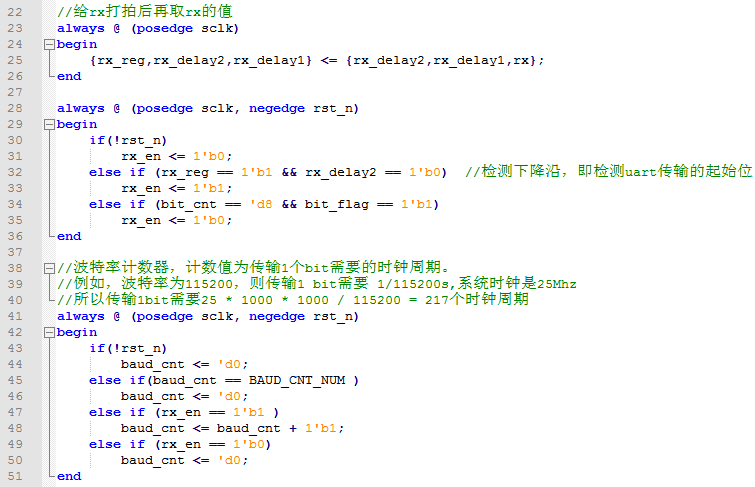

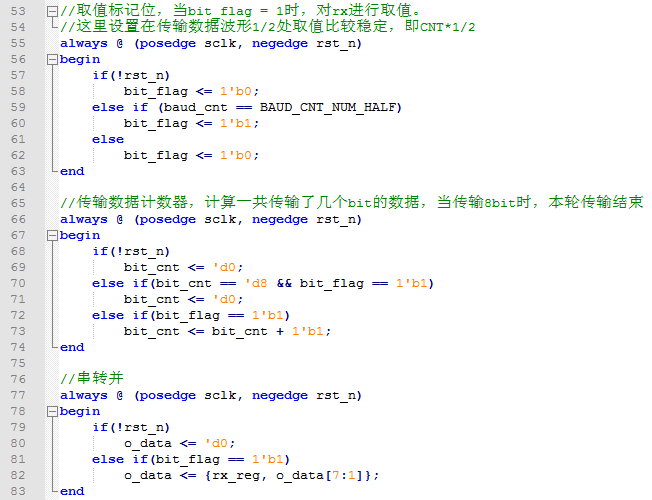

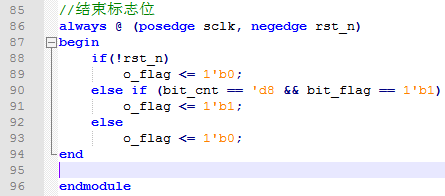

1. Rx端

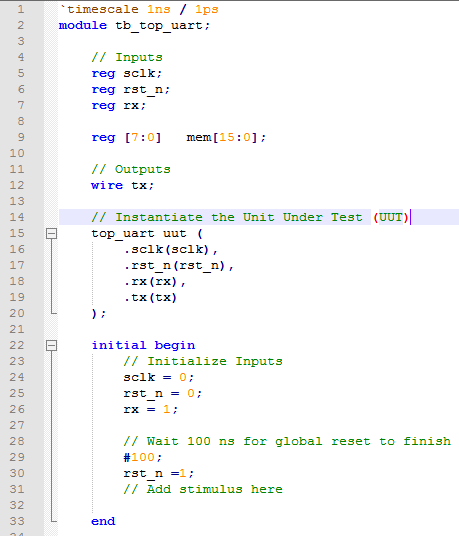

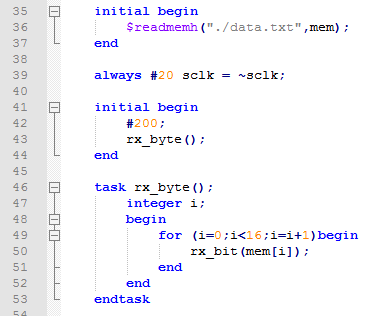

本次仿真使用到了task语句,task语句通常在当仿真时需要给输入变量特定的输入值时使用,例如本次仿真对rx端进行赋值。

3.6 仿真结果及问题排查

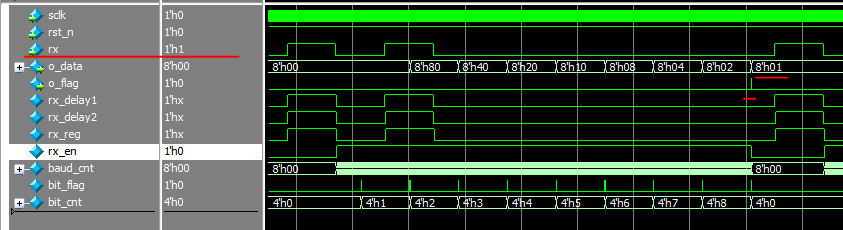

Rx端:

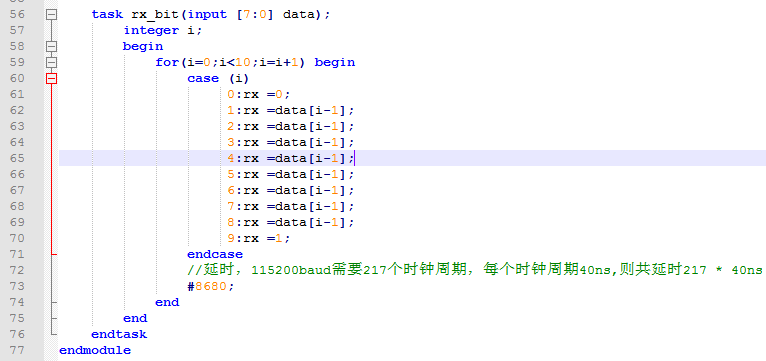

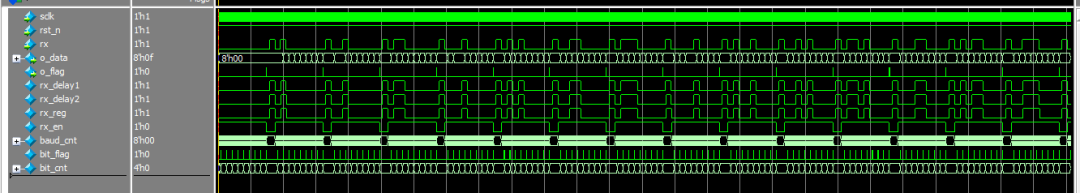

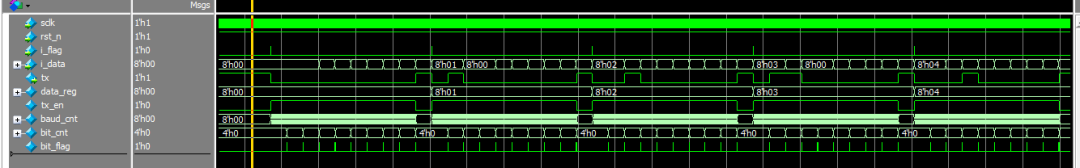

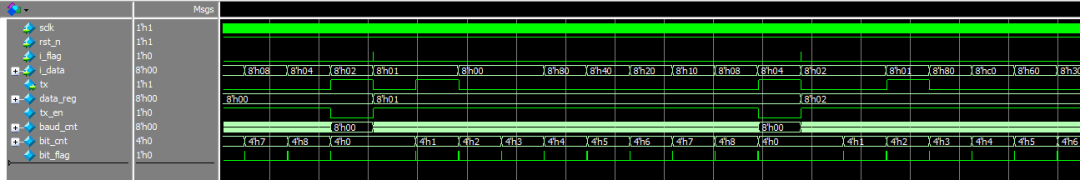

总体波型如图甲所示:

当rx=1时,读取的o_data多处理机系统统计数据在o_flag = 1(即说道数据传输收场)时也为1,結果很正常。

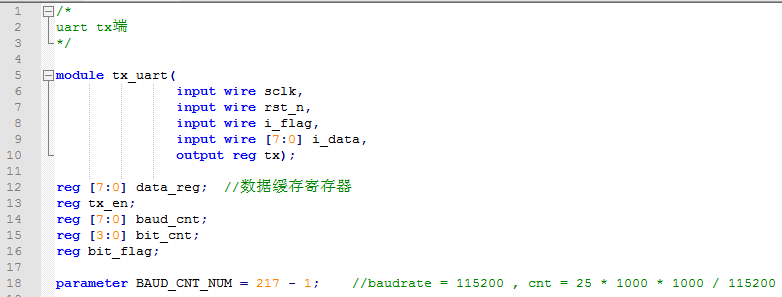

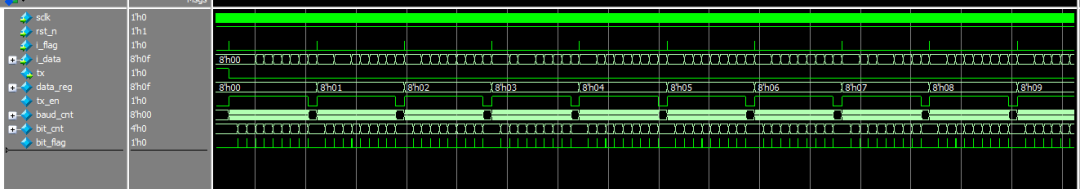

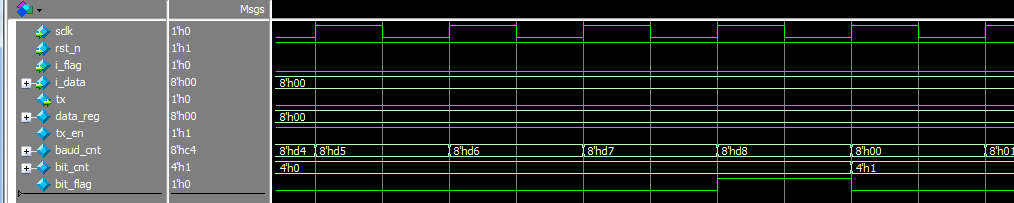

Tx端:

整体化波形参数一下:

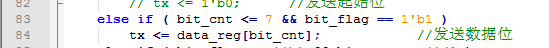

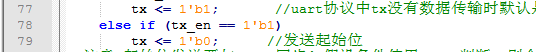

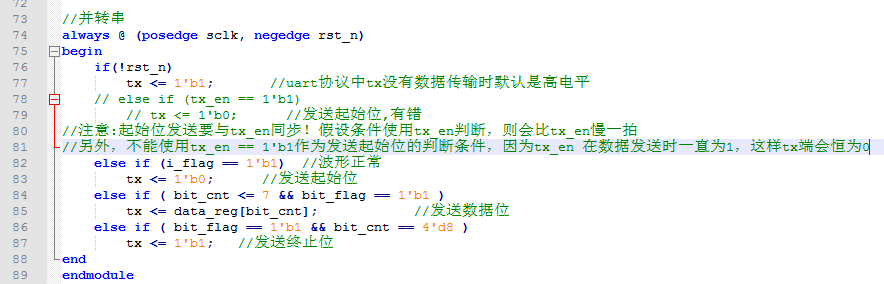

上图很明星还可以分辨出tx端网络文件传输有事情,当tx运输起讫位(即会降低)后,没了将数剧打出。测量的卫星信号波形图,总体正常情况。可以看到事情大概率计算造成在tx赋值一些,一会展开其实是运输数剧位的因素评判有事情,查验二维码,数剧网络文件传输时的评判因素正确:

起始位发送要与tx_en同步。假设条件使用tx_en判断,则会比tx_en慢一拍。

其它,不许应用tx_en == 1'b1做运送起讫位的评断状况,这是因为tx_en 在信息运送时总是为1,这类tx端会恒为0,获取后世码内容如下:

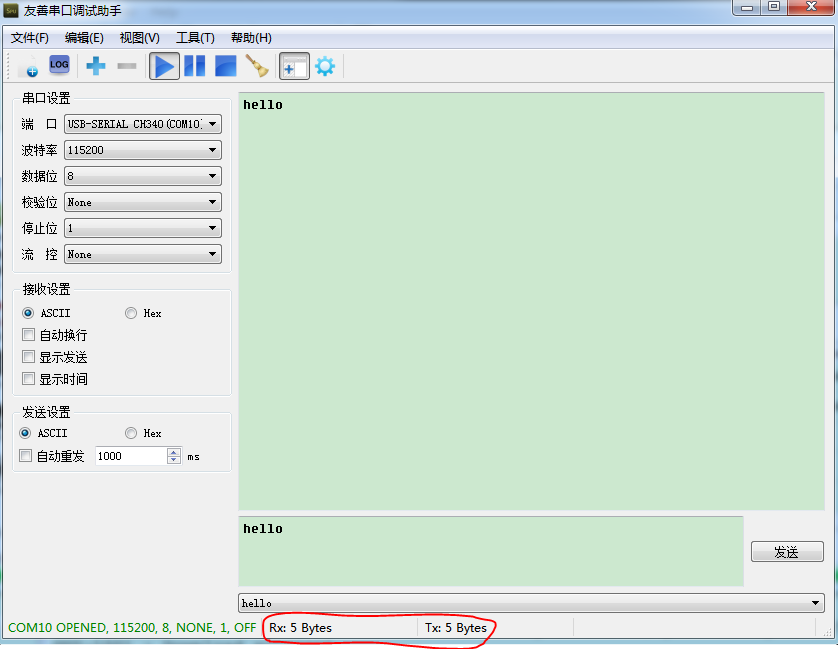

3.7 上板最终效果

源代码下载百度进开发设计板后,在串口程序调试小助手中能正确发收数据统计,以下的: